# VM6069

# **CUSTOM PROTOCOL INTERFACE**

# **USER'S MANUAL**

82-0041-000 Rev. April 7, 2003

VXI Technology, Inc.

2031 Main Street Irvine, CA 92614-6509 (949) 955-1894

VXI Technology, Inc.

# TABLE OF CONTENTS

#### INTRODUCTION

| Certification                                     |    |

|---------------------------------------------------|----|

| Warranty                                          |    |

| Limitation of Warranty                            |    |

| Restricted Rights Legend                          |    |

| DECLARATION OF CONFORMITY                         |    |

| GENERAL SAFETY INSTRUCTIONS                       |    |

| Terms and Symbols                                 |    |

| Warnings                                          |    |

| SUPPORT RESOURCES                                 |    |

| SECTION 1                                         |    |

| INTRODUCTION                                      |    |

| Introduction                                      |    |

| Description                                       |    |

| VM6069 Features                                   |    |

| SECTION 2                                         |    |

| PREPARATION FOR USE                               | 17 |

| Installation                                      |    |

| Calculating System Power and Cooling Requirements |    |

| Setting the Chassis Backplane Jumpers             |    |

| Setting the Logical Address                       |    |

| Front Panel Interface                             |    |

| SECTION 3                                         |    |

| Programming                                       |    |

| Introduction                                      |    |

| Interface FPGA                                    |    |

| User FPGA                                         |    |

| Register Access                                   |    |

| Flash Memory                                      |    |

| Flash - Read / Write                              |    |

| Downloading User FPGA Code / Data Pattern         |    |

| User FPGA Design                                  |    |

| User FPGA Design Guidelines                       |    |

| User FPGA Signal Description                      |    |

| VXI Register Address Decoding                     |    |

| VMIP Data Bus Interface                           |    |

| VXI Bus Acknowledge                               |    |

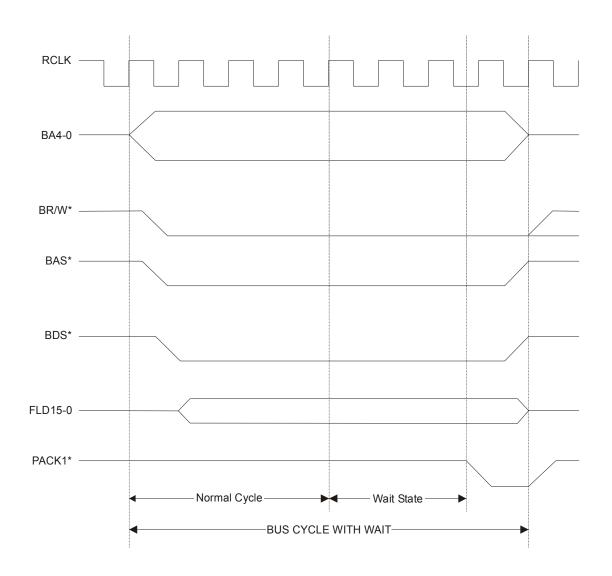

| VMIP Bus Timing                                   |    |

| Using the Interrupt Signal                        |    |

| Accessing Peripherals                             |    |

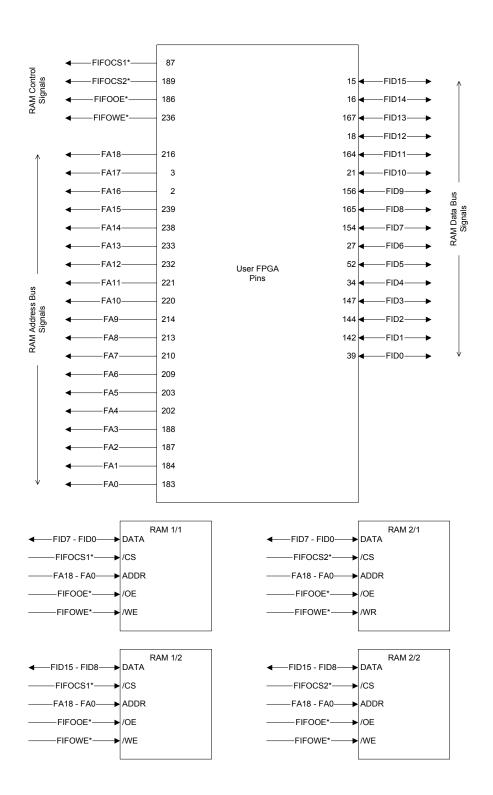

| SRAM                                              |    |

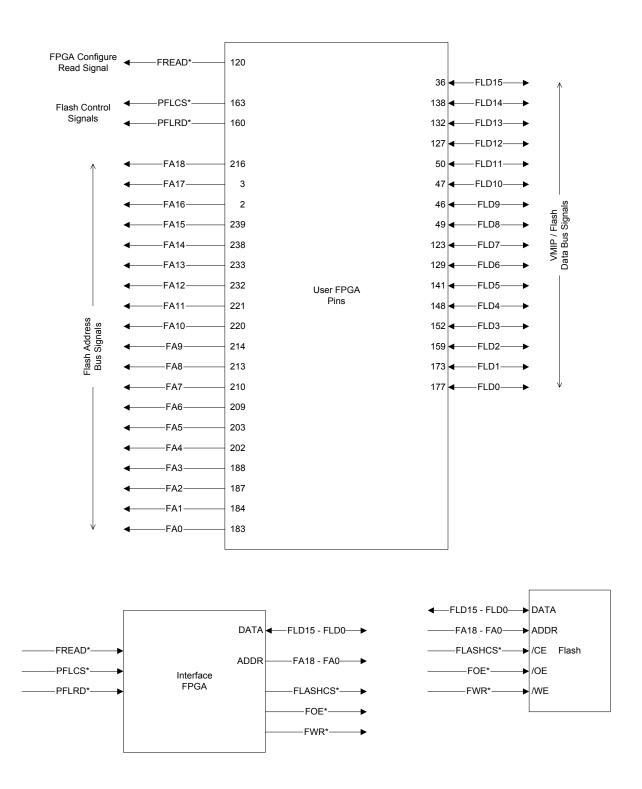

| Flash Memory                                      |    |

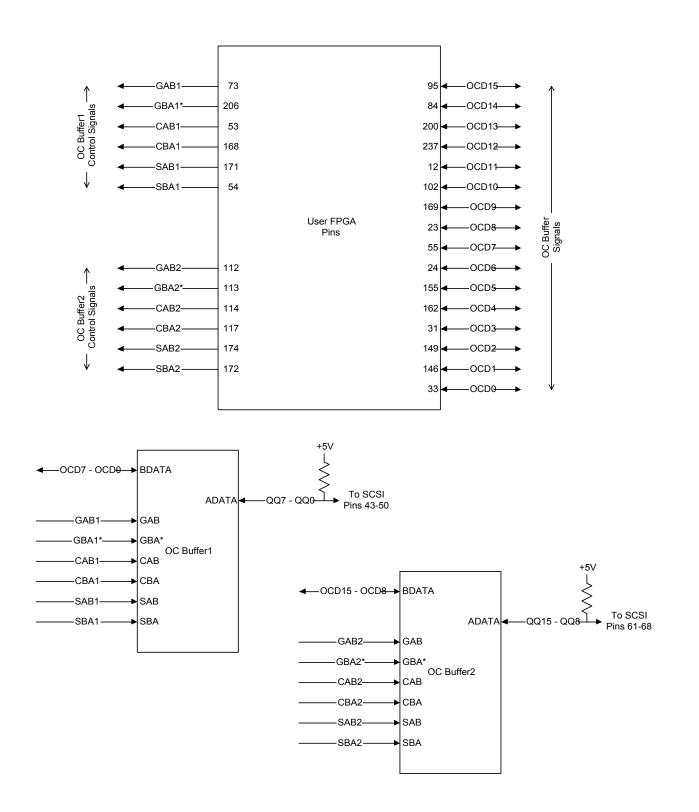

| Open Collector Buffers<br>SIPEX Transmitters      |    |

| SIPEX Receivers                                   |    |

| SIPEX Receivers                                   |    |

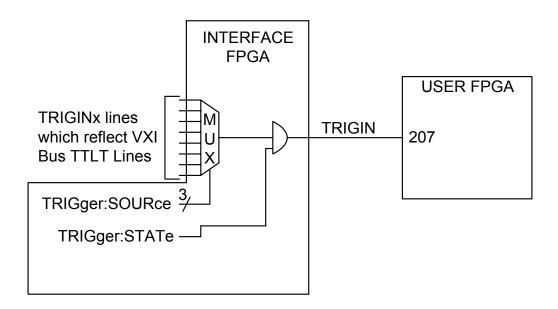

| VXI Bus TTL Trigger Input                         |    |

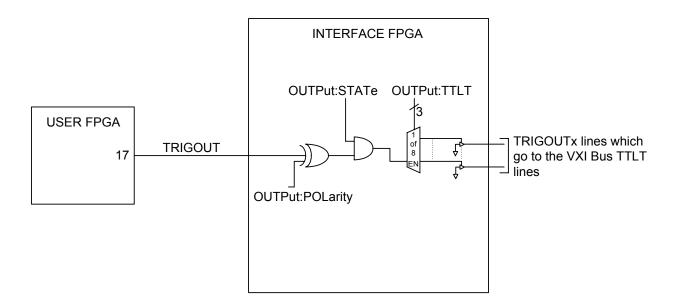

| VXI Bus TTL Trigger Output                        |    |

| SECTION 4                                         |    |

| COMMAND DICTIONARY                                |    |

| Introduction                                      |    |

| Programming                                       |    |

| 1 togramming                                      |    |

| Notation                                                    |        |

|-------------------------------------------------------------|--------|

| Alphabetical Command Listing                                |        |

| Command Dictionary                                          |        |

| IEEE 488.2 COMMON COMMANDS                                  |        |

| *CLS                                                        |        |

| *ESE                                                        | 64     |

| *ESR?                                                       |        |

| *IDN?                                                       |        |

| *OPC                                                        |        |

| *RST                                                        |        |

| *SRE                                                        |        |

| *STB?                                                       |        |

| *TRG                                                        |        |

| *TST?                                                       |        |

| *WAI                                                        |        |

| INSTRUMENT SPECIFIC SCPI COMMANDS                           |        |

| CALibration:SECure:CODE                                     |        |

| CALibration:SECure[:STATe]                                  |        |

| OUTPut[:STATe]                                              |        |

| OUTPut:TTLTrg                                               |        |

| OUTPut[:TTLTrg]:POLarity                                    |        |

| PROGram:MODule                                              |        |

| TRIGger:SOURce:TTLTrg                                       |        |

| TRIGger[:STATe]                                             |        |

| REQUIRED SCPI COMMANDS                                      |        |

| STATus:OPERation:CONDition?                                 |        |

| STATUS:OFERation:EONDHON?                                   |        |

| STATUS:OFERation: ENABLE                                    |        |

|                                                             |        |

| STATUS: OPERation: PTR                                      |        |

| STATus:OPERation[:EVENt]?                                   |        |

| STATUS: PRESet                                              |        |

| STATus:QUEStionable:CONDition?                              |        |

| STATus:QUEStionable:ENABle                                  |        |

| STATus:QUEStionable[:EVENt]?                                |        |

| APPENDIX A - APPLICATION EXAMPLE                            |        |

| Sample Code                                                 |        |

| Memory Access                                               |        |

| SIPEX Latch                                                 |        |

| Open Collector Buffers                                      |        |

| Misc. Registers                                             |        |

| UF_STD.UCF                                                  |        |

| UF_STD.V                                                    |        |

| LOOPBACK CONNECTOR USED TO TEST VM6069                      |        |

| APPENDIX B - VM6069 SCHEMATIC                               |        |

| 50-0110-000 - SCHEMATIC, VM6069, UNIVERSAL SERIAL INTERFACE |        |

| DEX                                                         |        |

| DEX                                                         | •••••• |

www.vxitech.com

#### CERTIFICATION

VXI Technology, Inc. (VTI) certifies that this product met its published specifications at the time of shipment from the factory. VTI further certifies that its calibration measurements are traceable to the United States National Institute of Standards and Technology (formerly National Bureau of Standards), to the extent allowed by that organization's calibration facility, and to the calibration facilities of other International Standards Organization members.

#### WARRANTY

The product referred to herein is warranted against defects in material and workmanship for a period of three years from the receipt date of the product at customer's facility. The sole and exclusive remedy for breach of any warranty concerning these goods shall be repair or replacement of defective parts, or a refund of the purchase price, to be determined at the option of VTI.

For warranty service or repair, this product must be returned to a VXI Technology authorized service center. The product shall be shipped prepaid to VTI and VTI shall prepay all returns of the product to the buyer. However, the buyer shall pay all shipping charges, duties, and taxes for products returned to VTI from another country.

VTI warrants that its software and firmware designated by VTI for use with a product will execute its programming when properly installed on that product. VTI does not however warrant that the operation of the product, or software, or firmware will be uninterrupted or error free.

#### LIMITATION OF WARRANTY

The warranty shall not apply to defects resulting from improper or inadequate maintenance by the buyer, buyersupplied products or interfacing, unauthorized modification or misuse, operation outside the environmental specifications for the product, or improper site preparation or maintenance.

VXI Technology, Inc. shall not be liable for injury to property other than the goods themselves. Other than the limited warranty stated above, VXI Technology, Inc. makes no other warranties, express or implied, with respect to the quality of product beyond the description of the goods on the face of the contract. VTI specifically disclaims the implied warranties of merchantability and fitness for a particular purpose.

#### **RESTRICTED RIGHTS LEGEND**

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subdivision (b)(3)(ii) of the Rights in Technical Data and Computer Software clause in DFARS 252.227-7013.

VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509 U.S.A.

|                                               | OF CONFORMITY<br>rding to ISO/IEC Guide 22 and EN 45014                                                                                                                                                                |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MANUFACTURER'S NAME                           | VXI Technology, Inc.                                                                                                                                                                                                   |

| MANUFACTURER'S ADDRESS                        | 2031 Main Street<br>Irvine, California 92614-6509                                                                                                                                                                      |

| PRODUCT NAME                                  | Custom Protocol Interface                                                                                                                                                                                              |

| MODEL NUMBER(S)                               | VM6069                                                                                                                                                                                                                 |

| PRODUCT OPTIONS                               | All                                                                                                                                                                                                                    |

| PRODUCT CONFIGURATIONS                        | All                                                                                                                                                                                                                    |

| the Low Voltage Directive 73/23/EEC and t     | rementioned product conforms to the requirements of<br>he EMC Directive 89/366/EEC (inclusive 93/68/EEC)<br>The product has been designed and manufactured                                                             |

| SAFETY                                        | EN61010 (2001)                                                                                                                                                                                                         |

| EMC                                           | EN61326 (1997 w/A1:98) Class A<br>CISPR 22 (1997) Class A<br>VCCI (April 2000) Class A<br>ICES-003 Class A (ANSI C63.4 1992)<br>AS/NZS 3548 (w/A1 & A2:97) Class A<br>FCC Part 15 Subpart B Class A<br>EN 61010-1:2001 |

| The product was installed into a C-size VXI i | mainframe chassis and tested in a typical configuration.                                                                                                                                                               |

|                                               | s been designed to be in compliance with the relevant sections<br>g with all essential requirements of the Low Voltage Directive.                                                                                      |

| April 2003                                    | Jemy Tatton<br>Jerry Patton, QA Manager                                                                                                                                                                                |

VXI Technology, Inc.

# **GENERAL SAFETY INSTRUCTIONS**

Review the following safety precautions to avoid bodily injury and/or damage to the product. These precautions must be observed during all phases of operation or service of this product. Failure to comply with these precautions, or with specific warnings elsewhere in this manual, violates safety standards of design, manufacture, and intended use of the product.

Service should only be performed by qualified personnel.

#### TERMS AND SYMBOLS

These terms may appear in this manual:

| WARNING | Indicates that a procedure or condition may cause bodily injury or death.                         |

|---------|---------------------------------------------------------------------------------------------------|

| CAUTION | Indicates that a procedure or condition could possibly cause damage to equipment or loss of data. |

These symbols may appear on the product:

ATTENTION - Important safety instructions

Frame or chassis ground

#### WARNINGS

Follow these precautions to avoid injury or damage to the product:

| Use Proper Power Cord   | To avoid hazard, only use the power cord specified for this product.                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Use Proper Power Source | To avoid electrical overload, electric shock or fire hazard, do<br>not use a power source that applies other than the specified<br>voltage. |

| Use Proper Fuse         | To avoid fire hazard, only use the type and rating fuse specified for this product.                                                         |

## WARNINGS (CONT.)

|   | Avoid Electric Shock | To avoid electric shock or fire hazard, do not operate this product with the covers removed. Do not connect or disconnect any cable, probes, test leads, etc. while they are connected to a voltage source. Remove all power and unplug unit before performing any service. <i>Service should only be performed by qualified personnel.</i>                                                                                                                                 |

|---|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Ground the Product   | This product is grounded through the grounding conductor of<br>the power cord. To avoid electric shock, the grounding<br>conductor must be connected to earth ground.                                                                                                                                                                                                                                                                                                       |

|   | Operating Conditions | <ul> <li>To avoid injury, electric shock or fire hazard:</li> <li>Do not operate in wet or damp conditions.</li> <li>Do not operate in an explosive atmosphere.</li> <li>Operate or store only in specified temperature range.</li> <li>Provide proper clearance for product ventilation to prevent overheating.</li> <li>DO NOT operate if any damage to this product is suspected. <i>Product should be inspected or serviced only by qualified personnel.</i></li> </ul> |

| ) | Improper Use         | The operator of this instrument is advised that if<br>equipment is used in a manner not specified in this<br>manual, the protection provided by this equipment be<br>may be impaired.                                                                                                                                                                                                                                                                                       |

## **SUPPORT RESOURCES**

Support resources for this product are available on the Internet and at VXI Technology customer support centers.

#### **Internet Support**

E-mail: support@vxitech.com Web Address: http://www.vxitech.com

#### **Telephone Support (U.S.)**

- Tel: (949) 955-1894 West Coast (216) 447-8950 East Coast

- Fax: (949) 955-3041 West Coast (216) 447-8951 East Coast

#### VXI Technology Headquarters

Technical Support VXI Technology, Inc. 2031 Main Street Irvine, CA 92614-6509

Tel: (949) 955-1894 Fax: (949) 955-3041

VXI Technology, Inc.

# **SECTION 1**

## INTRODUCTION

#### INTRODUCTION

The VM6069 is a Custom Protocol Interface that provides various I/Os that are programmed and controlled by the User FPGA. It provides easy interface design to the VXIbus so that the User FPGA code can be designed, accessed and controlled by device dependent registers.

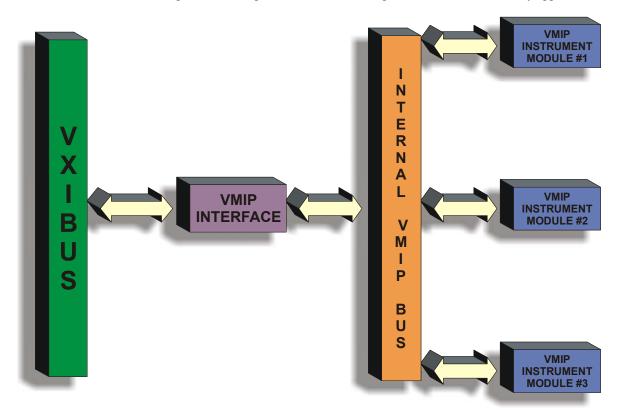

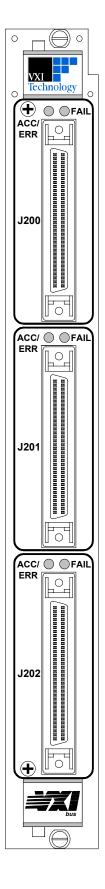

The most powerful feature of the VM6069 is that it is a member of the VXI Technology VMIP<sup>™</sup> (*VXI Modular Instrumentation Platform*) family of VXIbus. This gives the user the added flexibility of combining it with other instruments, such as digital multimeters or digitizers, to create a multi-function C-size card. The VM6069 may be combined with any of the other members of the VMIP family to form a customized and highly integrated instrument (see Figure 1-1). This allows the user to reduce system size and cost by combining the VM6069 with two other instrument functions in a singlewide C-size VXIbus module. Up to three VM6069s can also be combined together on a single VXIbus card, making it an ideal choice for many applications.

FIGURE 1-1 VMIP PLATFORM

#### DESCRIPTION

The VM6069 Custom Protocol Interface can be used in standard and non-standard protocol interfacing, where the hardware remains the same, and the FPGA program changes for each interface.

The protocol to be executed by this card can be downloaded to flash memory from the VXI controller through registers. At power-up, the User FPGA loads itself from flash memory. Module control and module status are done through the registers. All registers are mapped to device dependent registers.

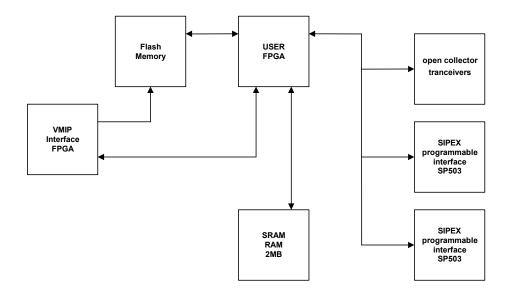

The heart of the VM6069 is the User FPGA, which can be modified over the VXIbus backplane. Logic patterns are created to make the VM6069 conform to a desired protocol and downloaded to flash memory on the VM6069. There is 512k of on-board Flash memory; 64k is used for the User FPGA patterns and the remainder is available to the VM6069 for other user-defined pattern. The User FPGA is also supported by two Mbytes of RAM for data reception and transmission. There are three types of electrical interfaces that can be manipulated by the User FPGA:

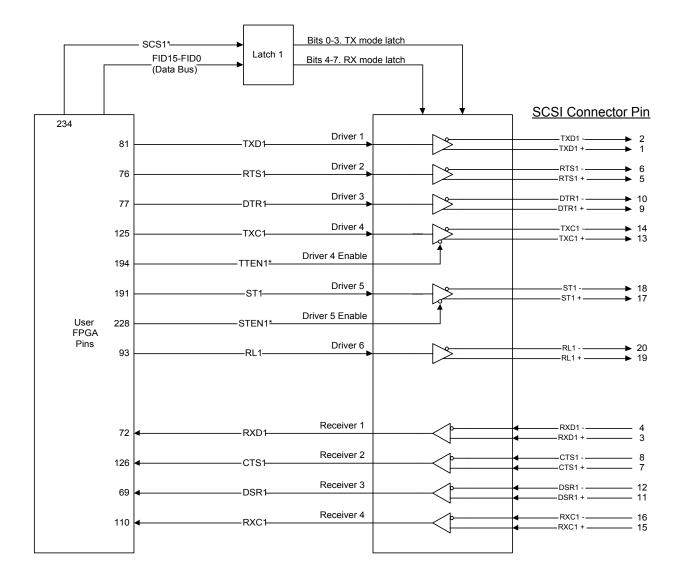

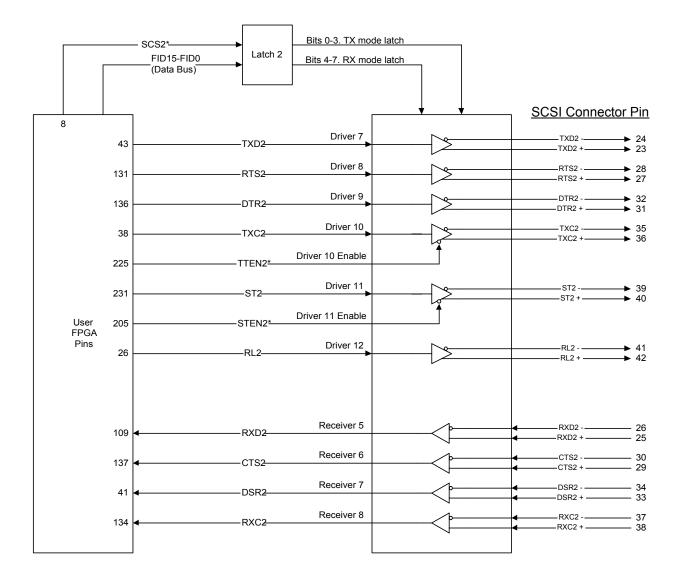

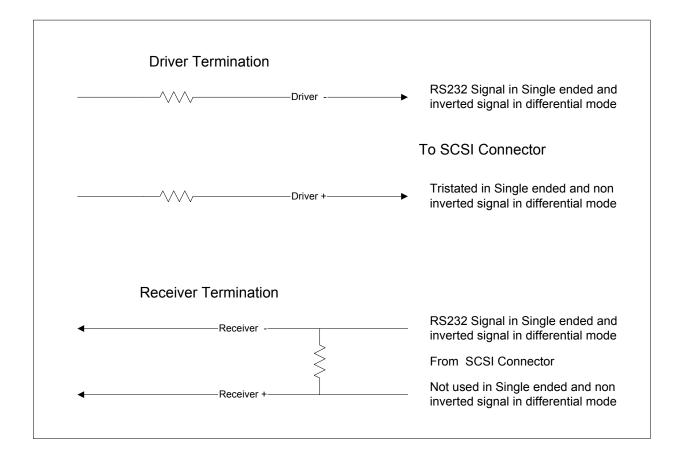

- Two programmable multi-mode serial transceivers: RS232, RS422, RS449, RS485, V35, and EIA530. These two programmable interfaces can be used as two standard serial interface channels; or, a total of twelve differential drivers and eight differential receivers can be manipulated by the User FPGA.

- Two 8-bit open collector transceivers controlled as either input or output on an 8-bit basis.

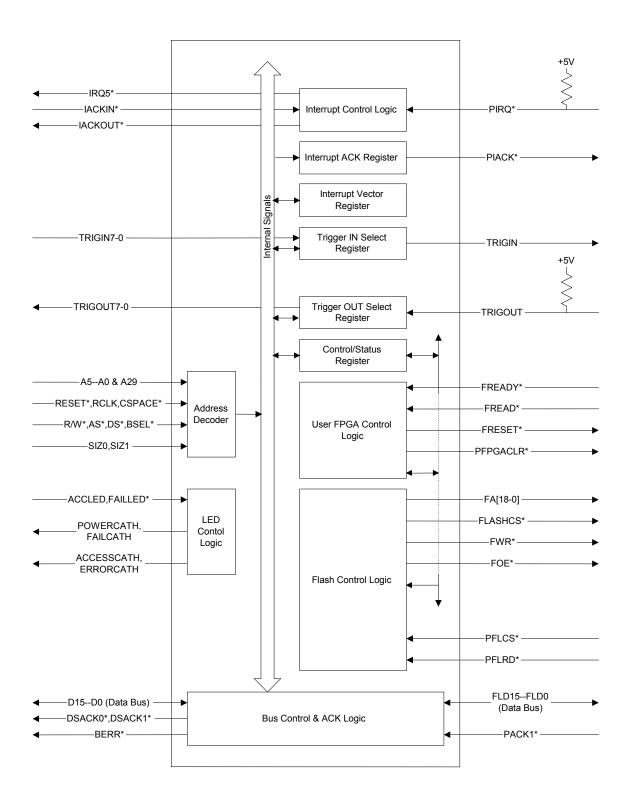

FIGURE 1-2 VM6069 BLOCK DIAGRAM

### VM6069 FEATURES

| FEATURES                  |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| INTERFACE FPGA            |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                           | Provides startup and control interface to the User FPGA. Provides controls to download or read flash memory.                                                                                                                                                                                                                                                                                    |  |

| FLASH MEMORY              |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                           | Flash memory has 4 Mbits of memory. It is split into a code and data area. In the code area, the User FPGA code is loaded. In the data area, user defined data patterns can be loaded. Flash memory is written from the VXIbus via the Interface FPGA.                                                                                                                                          |  |

| USER FPGA                 |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                           | The User FPGA is the heart of the system and provides the hardware interface<br>to all the peripherals and memory. This also has buffered VMIP signals so that<br>the device dependent registers can access it. On power up, it reads the<br>configuration from flash code memory automatically. The User FPGA can<br>read the data area of flash memory if the user designs his code to do so. |  |

| SRAM                      |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                           | Static RAM has 2 MB of memory. Both word and byte access is possible. Use of this memory depends on the User FPGA design code.                                                                                                                                                                                                                                                                  |  |

| Peripherals               |                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                           | The VM6069 provides various flexible I/Os. The use of these I/Os depends on the User FPGA code design.                                                                                                                                                                                                                                                                                          |  |

| SIPEX Drivers & Receivers | There are twelve drivers and eight receivers. They can be configured in RS232/RS422 and RS485.                                                                                                                                                                                                                                                                                                  |  |

| Open Collector I/O        | There are sixteen open collector I/Os that are byte configurable in input or output mode.                                                                                                                                                                                                                                                                                                       |  |

| User FPGA                      | ✓ 13k gates. Xilinx XC4013XL                                                                                                                                                |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RAM                            | ✓ 2 Mbytes                                                                                                                                                                  |  |

| Serial Drivers/Receivers       | <ul> <li>✓ 12 drivers, 8 receivers</li> <li>✓ 2 channels. Sipex 503CF</li> <li>✓ 5 Mbs data rate</li> <li>✓ Programmable RS232, RS422, RS449, RS485, V35, EIA530</li> </ul> |  |

| Open Collector<br>Transceivers | <ul> <li>✓ 16 channels, programmable on an 8-bit basis as TTL inputs or open collector outputs</li> <li>✓ 10 MHz data rate</li> </ul>                                       |  |

## TABLE 1-1 VM6069 GENERAL SPECIFICATIONS

# **SECTION 2**

# **PREPARATION FOR USE**

#### INSTALLATION

When the VM6069 is unpacked from its shipping carton, the contents should include the following items:

VM6069 Custom Protocol Interface Module

(1)VM6069 Custom Protocol Interface Module User's Manual (this manual)

(2) 3 <sup>1</sup>/<sub>2</sub>" diskettes: VM6069 Flash Memory Load and sample code (VTI P/N 72-0025-000)

All components should be immediately inspected for damage upon receipt of the unit.

Once the VM6069 is assessed to be in good condition, it may be installed into an appropriate C-size or D-size VXIbus chassis in any slot other than slot zero. The chassis should be checked to ensure that it is capable of providing adequate power and cooling for the VM6069. Once the chassis is found adequate, the VM6069's logical address and the chassis' backplane jumpers should be configured prior to the VM6069's installation.

#### **CALCULATING SYSTEM POWER AND COOLING REQUIREMENTS**

The power and cooling requirements of the VM2601 are given in the specification table in Section 1 of this manual. It is imperative that the chassis provide adequate power and cooling for this module. Referring to the chassis user manual, confirm that the power budget for the system (the chassis and all modules installed therein) is not exceeded and that the cooling system can provide adequate airflow at the specified backpressure.

It should be noted that if the chassis cannot provide adequate power to the module, the instrument may not perform to specification or possibly not operate at all. In addition, if adequate cooling is not provided, the reliability of the instrument will be jeopardized and permanent damage may occur. Damage found to have occurred due to inadequate cooling will void the warranty on the instrument in question.

#### SETTING THE CHASSIS BACKPLANE JUMPERS

Please refer to the chassis operation manual for further details on setting the backplane jumpers.

#### SETTING THE LOGICAL ADDRESS

The logical address of the VM6069 is set by a single 8-position DIP switch located near the VMIP module's backplane connectors (this is the only switch on the module). The switch is labeled with positions 1 through 8 and with an ON position. A switch pushed toward the ON legend will signify a logic 1; switches pushed away from the ON legend will signify a logic 0. The switch located at position 1 is the least significant bit while the switch located at position 8 is the most significant bit. See Figure 2-1 for examples of setting the logical address switch.

|                 |                         | Switch<br>Position | Switch<br>Value |

|-----------------|-------------------------|--------------------|-----------------|

|                 |                         | 1                  | 1               |

| SET TO 4        | SET TO 8                | 2                  | 2               |

|                 |                         | 3                  | 4               |

|                 |                         | 4                  | 8               |

| ON              | ON                      | 5                  | 16              |

|                 |                         | 6                  | 32              |

| 1 2 3 4 5 6 7 8 | 1 2 3 4 5 6 7 8         | 7                  | 64              |

| SET TO 168      | SET TO 255<br>(Dynamic) | 8                  | 128             |

FIGURE 2-1 LOGICAL ADDRESS SWITCH SETTING EXAMPLES

The VMIP may contain three separate instruments and will allocate logical addresses as required by the VXIbus specification (revisions 1.3 and 1.4). The logical address of the instrument is set on the VMIP carrier. The VMIP logical addresses must be set to an even multiple of 4 <u>unless</u> <u>dynamic addressing is used</u>. Switch positions 1 and 2 must always be set to the OFF position. Therefore, only addresses of 4, 8, 12, 16, ...252 are allowed. The address switch should be set for one of these legal addresses and the address for the second instrument (the instrument in the center position) will automatically be set to the switch set address plus one; while the third instrument (the instrument in the lowest position) will automatically be set to the switch set address plus two. If dynamic address configuration is desired, the address switch should be set for a value of 255 (All switches set to ON). Upon power-up, the slot 0 resource manager will assign the first available logical addresses to each instrument in the VMIP module.

If dynamic address configuration is desired, the address switch should be set for a value of 255. (All switches set to ON). Upon power-up, the slot-0 resource manager will assign the first available logical addresses to each instrument in the VMIP module.

### FRONT PANEL INTERFACE

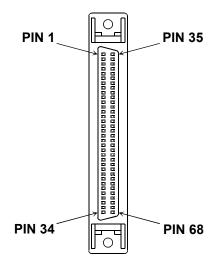

The peripheral I/Os are terminated at the high-density 68-pin SCSI connector.

Regardless of whether the VM6069 is configured with other VM6069 modules or with other VMIP modules, each interface is treated as an independent instrument in the VXIbus chassis. Each has its own Unique Logical Address and, as such, its own front panel ACCESS and FAIL indicators.

| SCSI Conn. Pin | Signal Name | SCSI Conn. Pin | Signal Name  |

|----------------|-------------|----------------|--------------|

| 1              | TXD1+ (OUT) | 35             | TXC2- (OUT)  |

| 2              | TXD1- (OUT) | 36             | TXC2+ (OUT)  |

| 3              | RXD1+(IN)   | 37             | RXC2- (IN)   |

| 4              | RXD1- (IN)  | 38             | RXC2+(IN)    |

| 5              | RTS1+(OUT)  | 39             | ST2- (OUT)   |

| 6              | RTS1- (OUT) | 40             | ST2+ (OUT)   |

| 7              | CTS1+(IN)   | 41             | RL2- (OUT)   |

| 8              | CTS1- (IN)  | 42             | RL2+ (OUT)   |

| 9              | DTR1+(OUT)  | 43             | R1IN+ (QQ0)  |

| 10             | DTR1- (OUT) | 44             | R1IN- (QQ1)  |

| 11             | DSR1+(IN)   | 45             | R2IN+(QQ2)   |

| 12             | DSR1- (IN)  | 46             | R2IN- (QQ3)  |

| 13             | TXC1+ (OUT) | 47             | R3IN+ (QQ4)  |

| 14             | TXC1- (OUT) | 48             | R3IN- (QQ5)  |

| 15             | RXC1+(IN)   | 49             | R4IN+ (QQ6)  |

| 16             | RXC1-(IN)   | 50             | R4IN- (QQ7)  |

| 17             | ST1+(OUT)   | 51             | (NC)         |

| 18             | ST1- (OUT)  | 52             | (NC)         |

| 19             | RL1+(OUT)   | 53             | (NC)         |

| 20             | RL1- (OUT)  | 54             | (NC)         |

| 21             | GND         | 55             | (NC)         |

| 22             | GND         | 56             | (NC)         |

| 23             | TXD2+ (OUT) | 57             | (NC)         |

| 24             | TXD2- (OUT) | 58             | (NC)         |

| 25             | RXD2+(IN)   | 59             | GND          |

| 26             | RXD2- (IN)  | 60             | GND          |

| 27             | RTS2+ (OUT) | 61             | DOUT1 (QQ8)  |

| 28             | RTS2- (OUT) | 62             | DOUT2 (QQ9)  |

| 29             | CTS2+(IN)   | 63             | DOUT3 (QQ10) |

| 30             | CTS2- (IN)  | 64             | DOUT4 (QQ11) |

| 31             | DTR2+ (OUT) | 65             | DOUT5 (QQ12) |

| 32             | DTR2- (OUT) | 66             | DOUT6 (QQ13) |

| 33             | DSR2+(IN)   | 67             | DOUT7 (QQ14) |

| 34             | DSR2- (IN)  | 68             | DOUT8 (QQ15) |

## TABLE 2-1 VM6069 CONNECTOR PINOUTS

The pin locations for J200, J201 and J202 are shown in Figure 2-3. Contact the factory for information on mating connectors.

FIGURE 2-3 J200, J201 AND J202 PIN LOCATIONS

VXI Technology, Inc.

# **SECTION 3**

## PROGRAMMING

#### INTRODUCTION

The VM6069 is a register-based module that allows for fast data throughput along the VXIbus backplane. The examples in this section show how to integrate customer-defined logic patterns with what is required to operate the VM6069. Services are also available through VXI Technology's custom engineering services to develop the VHDL/VERILOG code from protocol information.

The protocol to be executed by this card can be downloaded to flash memory from the VXI controller through the registers. The module control, module status and FIFO access are all done through the registers. These registers are mapped to device dependent registers.

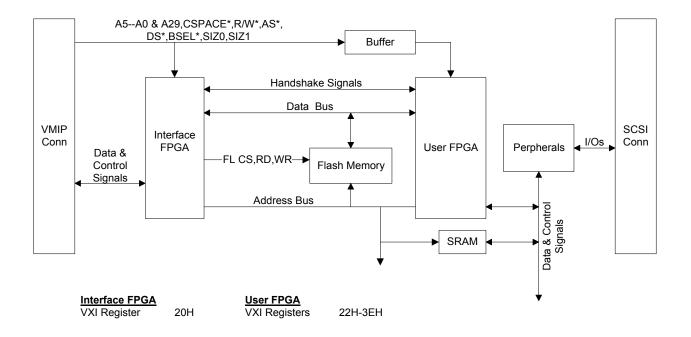

FIGURE 3-1 VM6069 UNIVERSAL SERIAL INTERFACE

#### **INTERFACE FPGA**

The Interface FPGA (QL2003-1TQFP144C) handles the interface between the VMIP and the VM6069. The Interface FPGA generates the necessary hand-shaking signals to the VMIP. It provides the VXIbus access to flash memory (AM29F040) for loading or changing the Protocol FPGA dynamically.

The figure on the next page describes the Interface FPGA design. The user can not change this design, it is given only for reference.

The Interface FPGA uses one register of the device dependent registers (20H). The rest of the device dependent registers (22H-3EH) may be decoded and used in the User FPGA design.

The Interface FPGA handles the VXI/VMIP and flash memory interface. It allows read/write access to flash memory from the VXI backplane. It also provides buffered VXI/VMIP signals to the User FPGA.

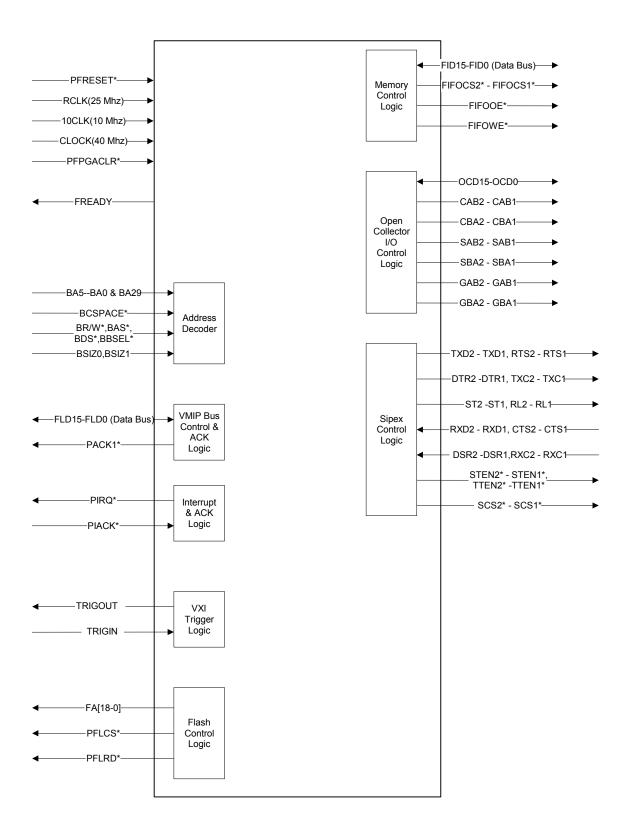

#### **USER FPGA**

The User FPGA (XILINX XC4013XL) is used for protocol execution. The configuration data for this device is loaded from flash memory by the master parallel configuration mode. This allows changing the VHDL/VERILOG design code dynamically for different protocol FPGA designs by loading flash memory through the VXIbus. The reset bit should be asserted and de-asserted after loading new VHDL/VERILOG design code to flash memory, which will force the device into configuration mode.

If the User FPGA has to transmit data, data would be written to SRAM through the VXIbus. The User FPGA then reads the data from SRAM and transmits it through the external interface.

If the User FPGA has to receive data, the User FPGA will receive the data from the external interface and then writes the data into SRAM. Data can then be read from SRAM through the VXIbus.

The 2 Mbytes of SRAM can be used as FIFO. The FIFO logic to interface the SRAM is emulated in the User FPGA.

FIGURE 3-2 VM6069 INTERFACE FPGA

#### **REGISTER ACCESS**

The module is accessed as a register-based VXI card. The device dependent registers (20H to 3EH) are available for use.

| Address in Hex | Function                                                      |  |

|----------------|---------------------------------------------------------------|--|

| 22 - 3E        | User FPGA Access Registers<br>(Depends on the User FPGA Code) |  |

| 20             | Interface FPGA Control / Status Register                      |  |

| 1E             |                                                               |  |

| 1C             |                                                               |  |

| 1A             |                                                               |  |

| 18             |                                                               |  |

| 16             | [ A32 Pointer Low ]                                           |  |

| 14             | [ A32 Pointer High ]                                          |  |

| 12             | [ A24 Pointer Low ]                                           |  |

| 10             | [ A24 Pointer High ]                                          |  |

| Е              | Data Low                                                      |  |

| С              | Data High                                                     |  |

| А              | Response [/Data Extended]                                     |  |

| 8              | Protocol [/Signal] Register                                   |  |

| 6              | [Offset Register]                                             |  |

| 4              | Status / Control Register                                     |  |

| 2              | Device Type                                                   |  |

| 0              | ID Register                                                   |  |

## TABLE 3-1 A16 Address Space - Register Map

| Bit   | Function                             |                                        | Access Type  |

|-------|--------------------------------------|----------------------------------------|--------------|

| 0 - 7 | Flash Data (Bit-                     | Flash Data (Bit-0 is D0 / Bit-7 is D7) |              |

| 8     | User FPGA Ready                      | 1 Ready, 0 Not Ready                   | Read Only    |

| 9     | Reset User FPGA                      | 1 Reset, 0 Not Reset                   | Read / Write |

| 10    | Clear User FPGA 1 Clear, 0 Not Clear |                                        | Read / Write |

| 11    | Code / Data Select                   | 1 Flash Code, 0 Flash Data             | Read / Write |

| 12-15 | See Table 3-3                        |                                        |              |

## TABLE 3-2 CONTROL / STATUS REGISTER (20H)

| User FPGA Ready:    | This bit is high once the User FPGA reads flash memory and configures itself. A low on this bit indicates that the User FPGA configuration has not been completed. Configuration failure may be caused by the following:                                                                                   |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | <ol> <li>Flash memory does not have the valid code for the User FPGA.</li> <li>An electrical fault has occurred in the User FPGA related circuits.</li> </ol>                                                                                                                                              |

| Reset User FPGA:    | A high on this bit forces the User FPGA into a "sleep" mode and the next falling edge causes the User FPGA to read Flash memory and configure itself.                                                                                                                                                      |

| Clear User FPGA:    | This is similar to the Reset User FPGA bit, but its use depends on the User FPGA design. Writing to this bit causes a low going pulse on the PFPGACLR* signal to the User FPGA. This can be used as a system reset in the User FPGA design; however, it does not force the User FPGA to read flash memory. |

| Code / Data Select: | A high on this bit selects the lower half of flash memory, and a low on this bit selects the upper half of flash memory. The FPGA design code needs to be loaded into the lower half of flash memory.                                                                                                      |

| Flash Data:         | When a write is made, these bits (one byte) are written to flash memory. When a read is made, these bits read flash memory data. See the next table for addressing flash memory.                                                                                                                           |

| Bits 12 to 15 for Flash Access Control from VXIbus |           |           |           |           |                                                   |              |

|----------------------------------------------------|-----------|-----------|-----------|-----------|---------------------------------------------------|--------------|

| Hex<br>Value                                       | Bit<br>15 | Bit<br>14 | Bit<br>13 | Bit<br>12 | Function Access Type                              |              |

| 0                                                  | 0         | 0         | 0         | 0         | No Access for VXI Bus Read / Write                |              |

| 1                                                  | 0         | 0         | 0         | 1         | Reset Address Counter - see note Read / Write     |              |

| 2                                                  | 0         | 0         | 1         | 0         | Increment Address Counter - see note Read / Write |              |

| 3                                                  | 0         | 0         | 1         | 1         | Spare 1 Read / Write                              |              |

| 4                                                  | 0         | 1         | 0         | 0         | Access Sequential Address                         | Read / Write |

| 5                                                  | 0         | 1         | 0         | 1         | Access Address 5555H                              | Read / Write |

| 6                                                  | 0         | 1         | 1         | 0         | Access Address 2AAAH Read / Write                 |              |

| 7                                                  | 0         | 1         | 1         | 1         | Spare 2                                           | Read / Write |

| 8                                                  | 1         | 0         | 0         | 0         | Sector 0 - Addr 00000-0FFFF                       | Read / Write |

| 9                                                  | 1         | 0         | 0         | 1         | Sector 1 - Addr 10000-1FFFF                       | Read / Write |

| Α                                                  | 1         | 0         | 1         | 0         | Sector 2 - Addr 20000-2FFFF                       | Read / Write |

| В                                                  | 1         | 0         | 1         | 1         | Sector 3 - Addr 30000-3FFFF                       | Read / Write |

| С                                                  | 1         | 1         | 0         | 0         | Sector 4 - Addr 40000-4FFFF                       | Read / Write |

| D                                                  | 1         | 1         | 0         | 1         | Sector 5 - Addr 50000-5FFFF                       | Read / Write |

| Ε                                                  | 1         | 1         | 1         | 0         | Sector 6 - Addr 60000-6FFFF                       | Read / Write |

| F                                                  | 1         | 1         | 1         | 1         | Sector 7 - Addr 70000-7FFFF                       | Read / Write |

### TABLE 3-3 CONTROL / STATUS REGISTER (20H) - BITS 12-15

These bits are used to access the flash memory. For normal operation (for the User FPGA to function), the **No Access for VXI Bus** function needs to be selected. A flash load utility is provided to download the User FPGA design (.EXO format) to flash memory. The utility loads the design into the lower half of flash memory. The user defined pattern (data that is not part of the design) needs to be loaded into the upper half of flash memory. Refer to this table to access the upper half of flash memory.

- **No Access for VXI Bus:** This disables access to flash memory from the VXI backplane. For normal module operation, these bits need to be zero.

- Addressing Flash Memory: A flash memory address is generated by the Interface FPGA when accessed from the VXI backplane. It uses the internal address counter (A0-A18 to access the flash memory. This address counter can be reset (resetting the address counter points it to the first location in flash memory), and incremented by writing to these bits. Only sequential flash memory access is available from the VXI backplane; however, two pre-defined address locations (5555H and 2AAAH) can be accessed independent of the address counter (see above table). In addition, individual sectors can be selected independent of the address counter. This sector addressing is only useful for erasing the specified sector; it cannot be used to read or write to flash memory.

*NOTE:* Address counter reset and increment is done only when the bits are written to. If a read is done when these bits are set, it uses the current address to read the flash memory.

#### FLASH MEMORY

The flash memory (AM29F40) has 4M bit (524,228 x 8 bits) divided into eight sectors; each sector is 64KB. The User FPGA (XC4013XL) needs 393,623 bits of configuration data. This is less than one sector of the flash memory. Four sectors (0-3) are allocated for the User FPGA and four sectors (4-7) are allocated for data pattern storage. This means there are more than three sectors available for future expansion of the FPGA configuration.

#### FLASH - READ / WRITE

The flash memory address is generated by the Interface FPGA and it depends on the control/status register. The required control bits are provided to select the code/data memory area: to access the memory sequentially, and to access the memory in predefined addresses, so as to specify the various command sequences.

Erasing, downloading and reading flash can be done per the following sequence. Though multiple sectors can be erased simultaneously, each sector should be erased one at a time. The time between two sector addresses (to erase two sectors at once) is  $87\mu s$  max., which is too time constraining for most programming environments.

#### DOWNLOADING USER FPGA CODE / DATA PATTERN

The following steps explain the flash memory downloading sequence; however, it is recommended to use the software utility provided to download the User FPGA design (.EXO format) to flash memory.

- 1. Put the User FPGA in reset mode

- (a) Write 0200H to register 20H

- 2. Do Chip Reset

- (a) Write 42F0H to register 20H

- 3. Check Manufacturer Code and Device Code

- (a) Write 52AAH to register 20H Writes AAH to address 5555H

- (b) Write 6255H to register 20H Writes 55H to address 2AAAH

- (c) Write 5290H to register 20H Writes 90H to address 5555H

- (d) Write 1200H to register 20H *Reset the address counter (to select even address)*

address)

*The data should be 01H (manufacturer code)*

- (e) Read from register 20H

- (f) Write 2200H to register 20H Increment address counter (to become odd

- (g) Read from register 20H The data should be A4H (device code)

- 4. Do Chip Erase / Sector Erase

- (a) Write 1200H to register 20H Reset the address counter

- (b) Write 52AAH to register 20H Writes AAH to address 5555H

- (c) Write 6255H to register 20H

- (d) Write 5280H to register 20H

- (e) Write 52AAH to register 20H Writes AA

- (f) Write 6255H to register 20H Writ

- Writes 80H to address 5555H Writes AAH to address 5555H Writes 55H to address 2AAAH

Writes 55H to address 2AAAH

#### After step 4f, select one of the following steps - I, II or III - and proceed further:

- I. Erase all sectors Chip Erase

- (g) Write 5210H to register 20H Writes 10H to address 5555H

- (h) Read from register 20H

Check that data-bit 7 is '1'. Read data until data-bit 7 is '1'. After this step, go to step 5a.

Select sector 1, the data is 30H

II. Erase sectors 0-3 - For down loading code

Each sector has to be erased one by one. Send one erase command, poll the data to check that erasing is complete, and then erase the next sector. Pick one step from g - j, then do step k.

- (g) Write 8230H to register 20H Select sector 0, the data is 30H

- (h) Write 9230H to register 20H

- (i) Write A230H to register 20H Select sector 2, the data is 30H

- (j) Write B230H to register 20H Select sector 3, the data is 30H

- (k) Read from register 20H

Check that data-bit 7 is '1'. Read data until data- bit 7 is '1'. Do not change register 20H in the mean time because it has to poll the data in the same sector. If all the sectors (0-3) are erased proceed to step 5a else go back to step 4a

II. Erase sectors 4-7 - For down loading data

Each sector has to be erased one by one. Send one erase command, poll the data to check that erasing is complete, and then erase the next sector. Pick one step from g - j, then do step k.

- Write C230H to register 20HSelect sector 4, the data is 30H

- (h) Write D230H to register 20H Select sector 5, the data is 30H

- Write E230H to register 20HSelect sector 6, the data is 30H

- Write F230H to register 20HSelect sector 7, the data is 30H

- (k) Read from register 20H

(g)

(i)

(j)

Check that data-bit 7 is '1'. Read data until data- bit 7 is '1'. Do not change register 20H in the mean time because it has to poll the data in the same sector. If all the sectors (4-7) are erased proceed to step 5a else go back to step 4a

| 5. | Dow | vnload Code / Data                                                                                           |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|----|-----|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|    | (a) | Reset Flash Address Counter                                                                                  |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |     | Write 1200H to register 20H                                                                                  | Reset the address counter                                                                                                                                                                                          |  |  |  |  |  |  |

|    | (b) | Select Code Area or Data Area                                                                                |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |     | Write 0A00H to register 20H                                                                                  | To select code area                                                                                                                                                                                                |  |  |  |  |  |  |

|    |     | Write 0200H to register 20H                                                                                  | To select data area                                                                                                                                                                                                |  |  |  |  |  |  |

|    |     | Choose either the <u>code area</u> or the <u>data area</u> .                                                 |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |     | Both areas are not simultaneously available.                                                                 |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    | (c) | Send program command                                                                                         |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |     | Write 52AAH to register 20H                                                                                  | Writes AAH to address 5555H                                                                                                                                                                                        |  |  |  |  |  |  |

|    |     | Write 6255H to register 20H                                                                                  | Writes 55H to address 2AAAH                                                                                                                                                                                        |  |  |  |  |  |  |

|    |     | Write 52A0H to register 20H                                                                                  | Writes A0H to address 5555H                                                                                                                                                                                        |  |  |  |  |  |  |

|    | (d) | Write single byte to current address                                                                         |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |     | Write 42XXH to register 20H                                                                                  | Where XX is the data                                                                                                                                                                                               |  |  |  |  |  |  |

|    | (e) | Poll the data from the current addr                                                                          | ress                                                                                                                                                                                                               |  |  |  |  |  |  |

|    |     | Read from register 20H                                                                                       | Bits D0-D7 represent the data. Check that data-<br>bit 7 is the same as the written bit. If they are not<br>the same, then read and check again. Continue<br>to poll the data until data-bit 7 is the same as that |  |  |  |  |  |  |

|    |     | of the written bit.                                                                                          |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    | (f) | Increment Address Counter                                                                                    |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |     | Write 2200H to register 20H                                                                                  | Increments the address counter                                                                                                                                                                                     |  |  |  |  |  |  |

|    | (g) | Continue step c.                                                                                             | Alternatively, if the download is completed, do a chip reset again (step 2).                                                                                                                                       |  |  |  |  |  |  |

| 6. | Rea | d back the data to check whether it i                                                                        | s written correctly.                                                                                                                                                                                               |  |  |  |  |  |  |

|    | (a) | Reset Flash Address Counter                                                                                  |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |     | Write 1200H to register 20H                                                                                  | Resets the address counter                                                                                                                                                                                         |  |  |  |  |  |  |

|    | (b) | Select Code Area or Data Area                                                                                |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |     | Write 0A00H to register 20H                                                                                  | To select code area                                                                                                                                                                                                |  |  |  |  |  |  |

|    |     | Write 0200H to register 20H                                                                                  | To select data area                                                                                                                                                                                                |  |  |  |  |  |  |

|    |     | Choose either the <u>code area</u> or the <u>data area</u> .<br>Both areas are not simultaneously available. |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    | (c) | Send Read / Reset Command                                                                                    |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |     | Write 52AAH to register 20H                                                                                  | Writes AAH to address 5555H                                                                                                                                                                                        |  |  |  |  |  |  |

|    |     | Write 6255H to register 20H                                                                                  | Writes 55H to address 2AAAH                                                                                                                                                                                        |  |  |  |  |  |  |

|    |     | Write 52F0H to register 20H                                                                                  | Writes F0H to address 5555H                                                                                                                                                                                        |  |  |  |  |  |  |

|    | (d) | Read single byte from current address                                                                        |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |     | Read from register 20H                                                                                       | Bits D0-D7 represent the data                                                                                                                                                                                      |  |  |  |  |  |  |

|    | (e) | Compare the data with the written data                                                                       |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    | (f) | Increment the Address Counter                                                                                |                                                                                                                                                                                                                    |  |  |  |  |  |  |

|    |     | Write 2200H to register 20H                                                                                  | Increments the address counter                                                                                                                                                                                     |  |  |  |  |  |  |

|    | (g) | Continue step d.                                                                                             | Alternatively, if the comparison (read) is completed, then do a chip reset again (step 2).                                                                                                                         |  |  |  |  |  |  |

- 7. Put the User FPGA in normal mode and set flash access bits to 'No Access for VXIbus' status.

- (a) Write 0000H to register 20H

#### Notes:

- 1. When reading from flash memory, steps d &f can be contiguous if the comparison is not required (i.e. to reach a particular address).

- 2. If only reading from flash is required, follow steps 1, 6a, 6b & 6c, then follow steps 6d to 6g to read the required code/data. Finish with steps 2 and 7.

- 3. Any digit represented by an XX indicates data to be written.

# **USER FPGA DESIGN**

The User FPGA is the heart of the system and provides the hardware interface to all the peripherals and memory. This also has buffered VMIP signals so that the device dependent registers can access it. On power-up, it reads the configuration from the flash code memory area and configures itself. The User FPGA can read the data area of flash memory if the user designs the code as such. The functioning of the board entirely depends on the User FPGA code that is designed by the user.

The User FPGA design is developed in VHDL/Verilog and converted to a **.EXO** hex file. This file is then downloaded to flash memory through the VXI backplane. A software utility is provided to download the **.EXO** hex file to flash memory. Since only a small area of flash memory is used for the User FPGA design, the rest of flash memory may be used to store user defined data.

#### **USER FPGA DESIGN GUIDELINES**

Use the following guidelines to get started with your User FPGA design:

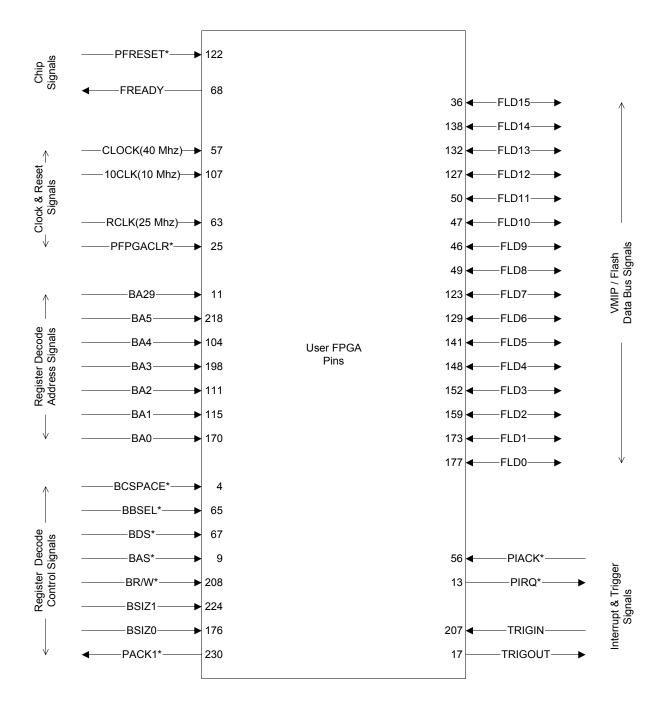

- 1. Familiarize yourself with the User FPGA signals see Table 3-4.

- 2. Familiarize yourself with the Interface FPGA, VMIP Interface, memory, Sipex latches and open collector buffers see figures in this section.

- 3. Convert your application requirement to Verilog/VHDL/schematics in the Xilinx foundation series or Alliance series.

- 4. The User FPGA design may make use of the memory, Sipex drivers, receivers or the open collector buffers:

- Note: It is necessary to generate a data transfer acknowledge whenever a VXI backplane access is made. If the module is accessed to any device dependent registers (22H 3EH), and the User FPGA does not acknowledge this, the front panel will indicate a system fail has occurred (red LED).

- 5. Down load the design to flash memory using the software utility provided.

- 6. Now the module is ready to function per the User Design loaded in flash memory.

- 7. Use registers 22H 3EH (per the design) to transfer information (memory, I/O, etc.) between the VXI backplane and the module.

FIGURE 3-3 USER FPGA

#### USER FPGA SIGNAL DESCRIPTION

The following table describes the User FPGA signals. Most of these signals are available for design use. The active low signal is marked with a 'N' or a '\*' (asterisk) symbol. The Signal Direction column indicates whether the signal is an input or an output:

I = Input to User FPGA O = Output from User FPGA

Pin numbers are listed respective to their signal names.

#### Signal Signal Name Pin No. Description **Comments** Direction On the rising edge of this signal, the User FPGA reads flash memory and configures itself. This pin is not available to the Reset signal for PFRESET\* 122 Ι the User FPGA **user.** The user design that needs a system reset can use the signal PFGACLR\* (see below). 25 MHz VMIP Any VMIP interface logic would use this RCLK 63 Ι clock clock for timing. 10 MHz VXI This is the VXI backplane clock for 10CLK 107 Ι clock general use. For high-speed applications, this clock can be used for control to access 40 MHz clock for peripherals. However, the 25 MHz clock CLOCK 57 Ι general use should still be used for the VMIP interface. This signal can be used to clear all the internal registers and user defined User FPGA Clear variables in the User FPGA. This signal PFPGACLR\* 25 Signal from the Ι is active low when the system reset is Interface FPGA low, or when the clear control bit is set in the control register. User FPGA read The User FPGA generates this signal during configuration. This pin is not FREAD\* 120 0 signal to the Interface FPGA available to the user. User FPGA The User FPGA generates this signal Ready signal to once it reads the code and configures FREADY 68 Ο the Interface itself. This pin is not available to the FPGA user. 218, 104, 198, VMIP Address Buffered VMIP address lines for register BA5-BA0 & 111, 115, 170, Ι **BA29** address decoding. lines 11 VMIP signal for Buffered. Must be high for address BCSPACE\* 4 Ι address decoding decoding.

## TABLE 3-4 USER FPGA SIGNALS

### User FPGA Signals – (Cont.)

| Signal Name  | Pin No.                                                                               | Signal<br>Direction | Description                | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|---------------------------------------------------------------------------------------|---------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BR/W*        | 208                                                                                   | Ι                   | VMIP read/write signal     | Buffered. High for read, low for write.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BAS*         | 9                                                                                     | Ι                   | VMIP address<br>strobe     | Buffered. Should be low for address decoding.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| BDS*         | 67                                                                                    | Ι                   | VMIP data strobe           | Buffered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BBSEL*       | 65                                                                                    | Ι                   | VMIP board<br>select       | Buffered VMIP board select signal.<br>Should be low for address decoding.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BSIZ0, BSIZ1 | 176, 224                                                                              | Ι                   | VMIP bus width             | Buffered VMIP bus width signal for byte or word access.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| FLD15-FLD0   | 36, 138, 132,<br>127, 50, 47, 46,<br>49, 123, 129,<br>141, 148, 152,<br>159, 173, 177 | I/O                 | VMIP data bus              | Buffered.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

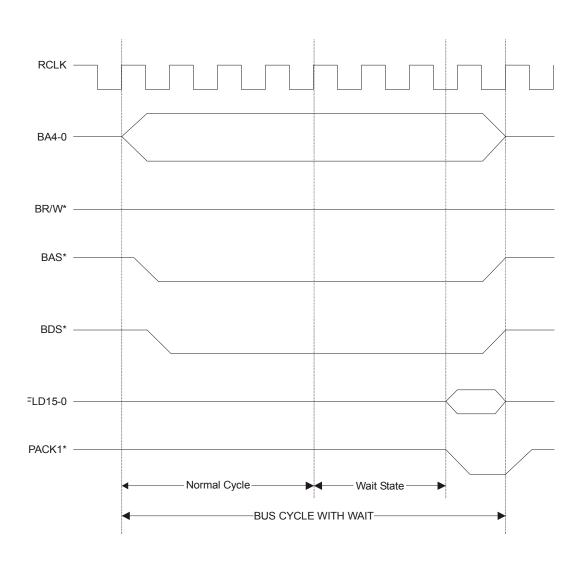

| PACK1*       | 230                                                                                   | Ο                   | Bus acknowledge            | Bus acknowledge signal to VMIP from<br>the User FPGA. The User FPGA should<br>generate this signal upon completion of<br>the data transfer between the VMIP and<br>the User FPGA. This signal should go<br>low within 20 RCLK clocks otherwise the<br>Interface FPGA will generate a time-out<br>and the current bus access is terminated.<br>The time-out signal lights the System Fail<br>LED and will remain lit until the next<br>system reset. However, further bus<br>access is allowed. |

| PIRQ*        | 13                                                                                    | О                   | Interrupt                  | This active low signal generates the<br>interrupt IRQ5 to the VMIP motherboard.<br>When the motherboard completes the<br>interrupt acknowledge cycle with the VXI<br>Controller end-software, the Interface<br>FPGA generates the PIACK* pulse signal<br>to the User FPGA.                                                                                                                                                                                                                     |

| PIACK*       | 56                                                                                    | Ι                   | Interrupt<br>acknowledge   | This signal is used as described above in the PIRQ* signal description.                                                                                                                                                                                                                                                                                                                                                                                                                        |